AMD在MCM多晶片封裝方面已經有了多年的實踐,而在3D封裝方面他們其實已經和臺積電有了許多合作,在今天的臺北電腦展釋出會的最後,AMD CEO Lisa Su博士宣佈了一項相當令人興奮的

2021-06-01 15:06:55

AMD在MCM多晶片封裝方面已經有了多年的實踐,而在3D封裝方面他們其實已經和臺積電有了許多合作,在今天的臺北電腦展釋出會的最後,AMD CEO Lisa Su博士宣佈了一項相當令人興奮的技術——3D Vertical Cache(3D垂直快取)。

‘

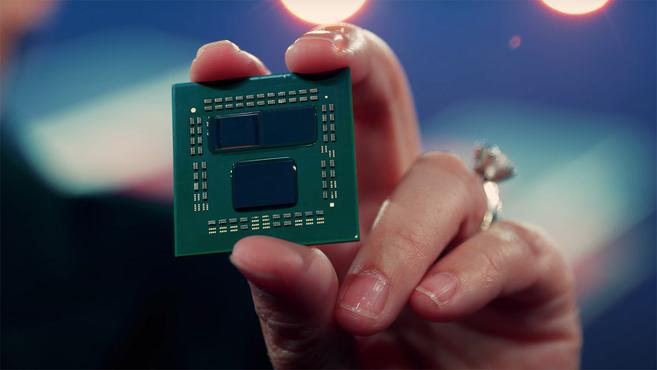

AMD把Chiplet封裝技術與晶片堆疊技術相結合,創造出了3D Chiplet架構,而3D垂直快取則是這技術的首個實踐。他們在現有的Zen 3架構銳龍5000處理器的CCD上再封進了一個64MB的7nm SRAM,這塊SRAM是直接堆疊CCD晶片上面的,這樣就能把每個CCD的L3快取容量從32MB增加到96MB,容量增加到原來的三倍。

SRAM與CCD之間通過矽通孔在堆疊的晶片之間傳輸訊號和電力,頻寬達到2TB/s,速度非常之快。由於採用了先進的工藝,這塊SRAM非常的薄,它兩邊添加了結構矽,組合之後的晶片做出一個無縫的表面,外觀上和現在的銳龍5000處理器是一模一樣的。

這塊就是採用3D堆疊技術的銳龍9 5900X處理器的原型設計,左邊的晶片上有一塊6mm*6mm的正方形SRAM與CCD結合在一起,在擁有雙CCD的12核或16核銳龍9處理器上就一共擁有192MB的L3快取。

在加入了3D垂直快取後,12核的Zen 3銳龍處理器在同頻下《戰爭機器5》的平均幀率提升了12%

整體遊戲效能提升了15%

AMD表示會在今年年底前會準備用3D chiplet生產一些高階產品,但沒有明說是什麼東西,不過有可能是銳龍5000XT系列處理器。

相關文章

AMD在MCM多晶片封裝方面已經有了多年的實踐,而在3D封裝方面他們其實已經和臺積電有了許多合作,在今天的臺北電腦展釋出會的最後,AMD CEO Lisa Su博士宣佈了一項相當令人興奮的

2021-06-01 15:06:55

果粉之家,專業蘋果手機技術研究十年!您身邊的蘋果專家~據彭博社報道,蘋果公司正在計劃繼續增加其經營的實體店數量,以此來擴大在全球的業務。蘋果公司目前在全球的零售店達到511

2021-06-01 15:06:51

近日,在北京國際摩托展上,鬆散旗下備受關注的SS SUMMER車型正式上市,新車共推出一款車型,售價28.8萬元,同此前的預售價格一致。新車最大的亮點是其復古的造型風格,定位多用途MPV,造

2021-06-01 15:06:15

燃氣灶是每個家庭不可缺少的廚房家電之一,一用就是幾年或者十幾年。因此,燃氣灶的使用壽命、火力、安全效能對於使用者的體驗感來說十分重要。今天,我們就來實測一下專為中式爆

2021-06-01 15:06:04

小米官方公佈了618的銷量資料,這家科技公司成為最活躍的品牌。官方透露僅用49分52秒就創收15億元。該品牌還透露,幾天前推出的Redmi Note 10 系列智慧手機在其國內首次銷售中,

2021-06-01 14:45:21

明敏 發自 凹非寺 量子位 報道 | 公眾號 QbitAI馬斯克又打臉了。此前聲稱2021年底就可能投入使用的海上火箭發射平臺,最早也要等到明年了。最近,他在推特上回應粉絲時透露:海上

2021-06-01 14:45:03